# U4301A PCIe Gen3 Analyzer

**User Guide**

## Notices

© Agilent Technologies, Inc. 2008-2012

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

### **Trademarks**

Microsoft®, MS-DOS®, Windows®, Windows 2000®, and Windows XP® are U.S. registered trademarks of Microsoft Corporation.

Adobe®, Acrobat®, and the Acrobat Logo® are trademarks of Adobe Systems Incorporated.

### **Manual Part Number**

U4301-97001

### **Edition**

February 2012

Available in electronic format only

Agilent Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

### **Safety Notices**

### CAUTION

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

## U4301A PCIe Gen3 Analyzer—At a Glance

The U4301A PCIe Gen3 analyzer lets you capture and decode PCI Express 3.0 (PCIe 3.0) data and view it in a Packet Viewer/Protocol Viewer window. The protocol analyzer supports all PCIe 3.0 speeds, including 2.5 GT/s (Gen1) and 5.0 GT/s (Gen2) through PCIe 8 GT/s (Gen3), and it supports link widths from x1 to x16.

The U4301A PCIe Gen3 analyzer is a module installed in an Agilent Digital Test Console chassis (for example, the U4002A portable 2-slot chassis) or Agilent AXIe chassis (for example, the M9502A 2 slot chassis).

When a controller PC is connected to an Agilent Digital Test Console chassis via an external PCIe interface and cable, the *Agilent Logic Analyzer* application (running on the controller PC) lets you connect to the chassis, set up U4301A PCIe Gen3 analyzer data captures, and perform analysis.

The U4301A PCIe Gen3 analyzer provides:

Effective presentation of protocol interactions from physical layer to transaction layer:

- Industry standard spreadsheet format protocol viewer with:

- Highlighting by packet type or direction.

- Easy flow columns to better understand the stimulus and response nature of the protocols.

- Context sensitive columns to show only the relevant information, minimizing the need to scroll horizontally.

- Flexible GUI configuration to meet debug needs, with pre-defined GUI layouts for Link Training debug, Config accesses, and general I/O.

Simple and powerful state-based triggering:

- New simple trigger mode makes it easy to setup single event triggers.

- Powerful state-based triggering including:

- Four states supported in trigger sequencer.

- Triggering on patterns (ordered set patterns or packet types).

- Internal counters and timers.

- Triggering on an ordered set on a specific lane.

- External trigger in/out.

Powerful hardware features ensure capture of important transition events:

- Dual phase lock loops (PLLs) per direction ensuring that the analyzer will lock on speed change events quickly and not miss any critical data.

- Large 4 GB of capture buffer per module (up to 8 GB of capture for x16 analyzer), for long recording sessions.

- PCIe Gen1 x4 link to the host PC, provides up to 10 Gbps of data download.

- LEDs to show lane status and speed for fast understanding of current link status.

- See "Using the PCIe Gen3 Analyzer" on page 5

## **Using the PCIe Gen3 Analyzer**

For an overview and list of features, see: "U4301A PCIe Gen3 Analyzer–At a Glance" on page 3  $\,$

- Chapter 1, "Hardware and Software Installation," starting on page 9

- Chapter 2, "Probing Options for PCIe Gen3," starting on page 11

- Chapter 3, "Specifying the Connection Setup," starting on page 13

- Chapter 4, "Setting the Capture Options," starting on page 25

- Chapter 5, "Tuning the Analyzer for a Specific DUT," starting on page 29

- Chapter 7, "Setting Up Triggers," starting on page 57

- Chapter 8, "Running/Stopping Captures," starting on page 67

- Chapter 9, "Viewing PCIe Gen3 Packets," starting on page 69

- See Also U4305 PCIe Gen3 exerciser documentation.

## Contents

U4301A PCIe Gen3 Analyzer—At a Glance 3

Using the PCIe Gen3 Analyzer 5

- **1** Hardware and Software Installation

- 2 Probing Options for PCIe Gen3

- **3** Specifying the Connection Setup

- **4** Setting the Capture Options

### 5 Tuning the Analyzer for a Specific DUT

PCIe Gen3 Tuning Overview 30 What is Tuning 30 How Tuning Works 30 When to Perform Tuning 30 **Default and User Defined .ptu Files** 31 Tuning - Broad steps 31 **Tuning Methods** 32 Preparing the Analyzer and DUT for Tuning 35 **Creating a Physical Layer Tuning File** 37 PCIe Gen3 Tuning Executable and its Usage 37 To create a physical tuning file 42 LEDs display during BER Based Tuning 43 Understanding "Minimum Time Between UFCs" and "UFC Burst Length" 43 How "Minimum Time Between UFCs" and "UFC Burst Length" is Used in LIDL 44 Tuning Tuning Time vs Eye Quality at Analyzer 45 Using the Tuning File in the Logic Analyzer GUI 46 Tuning a Bidirectional Setup 48 Fine Tuning a .ptu File 50 **Fine Tuning Flow** 50 To fine tune a .ptu file 50 Fine tuning - examples 51

Verifying a Tuning File 52

### 6 Manually Adjusting the Equalizing Snoop Probe (ESP) Settings

### 7 Setting Up Triggers

Setting Up Simple Triggers 58 Setting Up Advanced Triggers 61 Setting General Trigger Options 64 To select which links the trigger is for 64 To set the trigger position 64 To save/recall favorite triggers 65 To clear the current trigger 65

### 8 Running/Stopping Captures

### **9** Viewing PCIe Gen3 Packets

| Viewing the captured PCIe Traffic Statistics | 70 |

|----------------------------------------------|----|

| Exporting Captured PCIe Data to a .csv File  | 74 |

### **10 Glossary**

Index

U4301A PCIe Gen3 Analyzer User Guide

## **Hardware and Software Installation**

The U4301A PCIe Gen3 analyzer is a module installed in an Agilent Digital Test Console chassis (for example, the U4002A portable 2-slot chassis) or Agilent AXIe chassis (for example, the M9502A 2-slot chassis).

The Agilent chassis is connected to a controller PC via a PCI Express interface and cable.

The controller PC runs the *Agilent Logic Analyzer* application software which lets you set up the U4301A PCIe Gen3 analyzer, specify triggers and other data capture options, capture data, and analyze the captured data using Packet Viewer/Protocol Viewer windows.

See the earrow "Agilent Digital Test Console Installation Guide" for information on:

- Installing the U4301A PCIe Gen3 analyzer blade into a Digital Test Console chassis.

- Connecting the Digital Test Console chassis to a controller PC via the PCI Express Gen1 x4 interface.

- Installing the Agilent Logic Analyzer software on the controller PC.

See the  $\stackrel{\scriptstyle{\leftarrow}}{\sim}$  "Agilent AXIe based Logic Analysis and Protocol Test Modules Installation Guide" for information on:

- Installing the U4301A PCIe Gen3 analyzer module into an Agilent AXIe chassis.

- Connecting the AXIe chassis to a controller PC via the PCI Express interface.

- Installing the Agilent Logic Analyzer software on the controller PC.

### **1** Hardware and Software Installation

U4301A PCIe Gen3 Analyzer User Guide

# **Probing Options for PCIe Gen3**

The currently available options for probing a PCIe Gen3 device under test (DUT) are:

• U4321A solid slot interposer

2

- U4322A midbus 3.0 probe

- U4324A PCIe Gen3 Flying Lead probe

Details about these two probing options (and other PCIe Gen3 tools) can be found in the arrow "PCI Express Gen3 Hardware and Probing Guide".

## 2 Probing Options for PCIe Gen3

U4301A PCIe Gen3 Analyzer User Guide

## **Specifying the Connection Setup**

Once you have connected the U4301A module, probing hardware, and DUT in the required configuration based on your probing requirements, the next step is to configure the connection setup for the U4301A module in the Agilent Logic Analyzer application. You use the Connection Setup tab of the analyzer's Setup dialog to configure the connection setup.

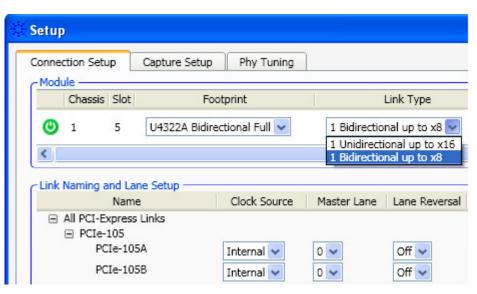

The connection setup details that you specify in this tab tells the Logic Analyzer software how the U4301A module is connected to the DUT in terms such as the probing option used, the direction of data capture (upstream, downstream, or bidirectional), and the link width needed. For instance, if you have connected the U4301A module hardware to the DUT using the U4321A Solid Slot Interposer card in a x8 bidirectional setup, then you need to select the U4321 Slot Interposer Both Dir x8 as the Footprint option, 1 Bidirectional upto x8 as the Link type, and x8 as the Link Width in the Connection Setup tab to reflect the hardware setup that you have configured.

### NOTE

- For details on how to set up the hardware and probing connections between the U4301A module and DUT, refer to PCI Express Gen3 Hardware and Probing Guide.

- For details on how to set up the chassis, U4301A module, and host PC, refer to the AXIe based Logic Analysis and Protocol Test Modules Installation Guide.

These guides are installed with the Logic Analyzer software and can also be downloaded from www.agilent.com.

### **Probing options**

While specifying the connection setup, one of the key requirements is to select the probing option that you have used with the U4301A module to probe the DUT and the data capture direction in which you have configured the hardware setup.

Broadly, there are the following four probing options available with the U4301A module:

- U4321A Solid Slot Interposer card

- U4322A Soft Touch Midbus 3.0 probe

- U4324A PCIe Gen3 Flying Lead probe

- PCIe Gen2 probes with the U4317A adapter. This adapter is used for conversion between the PCIe Gen2 probes and U4301A PCIe Gen3 Analyzer module. The PCIe Gen2 probes supported are:

- N5315A Solid Slot Interposer for PCIe Gen2

- N4241A straight, N4242A swizzled, and N4243A split cable Soft Touch Midbus 2.0 probe for PCIe Gen2

- N5328A Half Size Midbus probe

- N4241F/Z Flying Lead probe for PCIe Gen2

For each of the above four probing types, different options are available in the Connection Setup tab reflecting the data direction (upstream, downstream, or bidirectional). Upstream is the data direction towards the root complex. Downstream is the data direction away from the root complex. Based on your probing setup and the data capture direction in which you have configured the hardware setup, you need to select an appropriate probing option in the Connection Setup tab.

### **U4321A Solid Slot Interposer Card**

When used with a U4321A solid slot interposer card, one U4301A module can probe in the upstream (x1-x16), downstream (x1-x16), or bidirectional (x1-x8) way.

If you need to probe in both upstream as well downstream directions with a x16 link width, you need two U4301A Analyzer modules and a U4321A SSI card. To reflect such a hardware setup in the Connection Setup tab of the Logic Analyzer application, you need to select U4321A Slot Interposer Upstream as the probing option for one of the U4301A modules and U4321A Slot Interposer Downstream as the probing option for the other U4301A module.

if you have connected the U4301A module hardware to the DUT using the U4321A Solid Slot Interposer card in a x8 bidirectional setup, then you need to select the U4321 Slot Interposer Both Dir x8 as the probing option.

### U4322A Soft Touch Midbus 3.0 probe

The U4322A midbus 3.0 probes require footprints to be designed into the device under test. Each probe requires its own footprint, and there are basically two variations:

- **Bidirectional** where half the footprint pins are for the upstream data and the other half are for the downstream data.

- **Unidirectional** where all the pins on the footprint are for the data going in the same direction.

**Reversed** refers to optional lane reversal which is supported for upstream ports.

Based on how you have designed the footprint for the probe, you need to select an appropriate probing option in the Connection Setup tab. For instance, if you have configured a x4 bidirectional setup using a U4322A midbus probe, then you need to select U4322A Bidirectional Full as the Footprint, 1 Bidirectional upto x8 as the Link type, and x4 as the Link Width in the Connection Setup tab.

#### U4324A PCIe Gen 3 Flying Lead probe

When used with a U4324A Flying Lead probe, one U4301A module can probe in the upstream (x1-x16), downstream (x1-x16), or bidirectional (x1-x8) way. For x1-x8 bidirectional link type, you can use the U4324A Flying Lead probes in a straight or a swizzled configuration.

If you need to probe in both upstream as well downstream directions with a x16 link width, you need two U4301A Analyzer modules and eight U4324A Flying Lead probes. To reflect such a hardware setup in the Connection Setup tab of the Logic Analyzer application, you need to select the U4324A Flying Lead Probe as the probing option and Unidirectional as the link type for both the U4301A modules.

If you have connected the U4324A Flying Lead probes in a x1 to x8 bidirectional straight setup, then you need to select the U4324A Flying Lead Probe as the probing option and Bidirectional as the link type.

If you have set up a swizzled x1 to x8 bidirectional configuration using the U4324A Flying Lead probes, then you need to select the U4324A Flying Lead Probe Bi Swizzled as the probing option and Bidirectional as the link type.

### To specify the connection setup

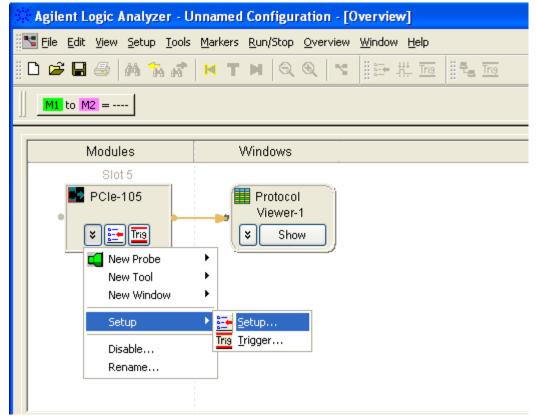

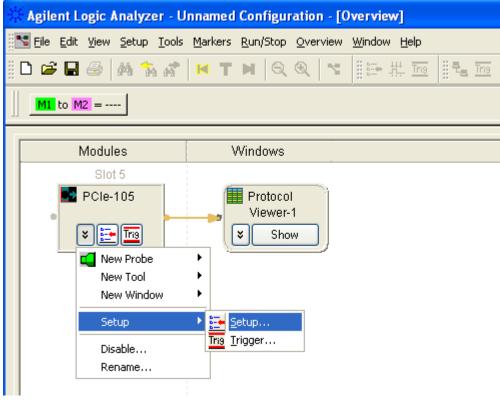

1 In the *Agilent Logic Analyzer* application's Overview window, from the PCIe analyzer module's drop-down menu, select **Setup>Setup...**.

|                                                                                     | rzer - Unnamed Configuration - [Overview]<br>p Iools Markers Run/Stop Overview Window Help |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

|                                                                                     | ₩ ₩ T N   Q @   %   E+ # Tm   % Tm   E+ Tm                                                 |

| M1 to M2 =                                                                          |                                                                                            |

| Modules                                                                             | Windows                                                                                    |

| Slot 5<br>PCIe-105<br>New Prot<br>New Too<br>New Win<br>Setup<br>Disable<br>Rename. | i                                                                                          |

| <u> </u>                                                                            | 7                                                                                          |

| Verview                                                                             | Protocol Viewer-1                                                                          |

| For Help, press F1                                                                  |                                                                                            |

2 From the **Footprint** listbox, select the type of probing that you have set up between the U4301A Analyzer module and DUT. For each of the supported four probing types, different probing options are available in the Footprints listbox based on the data direction (upstream, downstream, or bidirectional). Based on your probing setup and the link type needed, select an appropriate probing option from the Footprint listbox. Refer to the "Probing options" on page 13 to know more about these options.

| Setup            |                                                                                                                              |        |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--------|

| Connection Setup | Capture Setup Phy Tuning                                                                                                     |        |

| Link(s)          | Footprint                                                                                                                    |        |

| OPCIe-105        | U4324A Flying Lead Probe Bi Swizzled 💌                                                                                       |        |

| <                | U4321A Slot Interposer Upstream<br>U4321A Slot Interposer Downstream<br>U4321A Slot Interposer Both Dir x8                   |        |

| Nam              |                                                                                                                              | r Lane |

| PCIe-10          | U4324A Flying Lead Probe<br>U4324A Flying Lead Probe Bi Swizzled<br>N4241A+U4317A Gen2 Bidirectional                         |        |

| PCIe-10          | N4241A+U4317A Gen2 Unidirectional<br>N4241F/Z+U4317A Flying Lead Probe Uni<br>N4241F/Z+U4317A Flying Lead Probe Bi           |        |

|                  | N4242A+U4317A Gen2 Upstream<br>N4242A+U4317A Gen2 Downstream<br>N4243A+U4317A Gen2 Upstream<br>N4243A+U4317A Gen2 Downstream |        |

For more information on probing setups, click **Connection diagram...** or refer to the ightarrow "PCI Express Gen3 Hardware and Probing Guide".

If you have installed multiple U4301A modules in the chassis, all these modules are listed in the Module section of the tab. You need to select the probing option individually for these modules.

| Setup | p         |      |                              |                              |            |          |            |

|-------|-----------|------|------------------------------|------------------------------|------------|----------|------------|

|       | ction Set | qu   | Capture Setup Phy Tuning     |                              |            |          |            |

| Mod   | Chassis   | Slot | Footprint                    | Link Type                    | Link Width | Link(s)  | <b>ا</b>   |

| ۲     | 1         | 5    | U4321A Slot Interposer Ups 🔽 | 1 Unidirectional up to x16 🐱 | x1 🗸       | PCIe-105 | U4301 PCIe |

| ۲     | 1         | 4    | U4321A Slot Interposer Dov 🗸 | 1 Unidirectional up to x16 💌 | x1 💌       | PCIe-104 | U4301 PCIe |

| <     |           |      |                              |                              |            |          |            |

**3** Specify the link type.

The Link Type refers to the type of link that you want to create between the U4301A module and DUT. You can select the 1 Unidirectional up to x16 link type if you want the U4301A module to probe and capture data in only one direction (upstream or downstream). In the Unidirectional link type, the U4301A module can support a unidirectional link with upto 16 channels in the same direction. You can select the 1 Bidirectional up to x8 link type if you want the same U4301A module to probe and capture data in both directions (upstream as well as downstream). In the bidirectional link type, the U4301A module can support one bidirectional link with upto eight channels for each direction. When you select the bidirectional link type, two sub-links are created for the two directions. You can set the link attributes such as clock source, master lane, and lane ordering separately for these two sub-links. These attributes are available in the Link Naming and Lane Setup section.

The following screen displays the sub-links of a x8 bidirectional link. These sub-links have been renamed on the basis of the direction these represent.

| Connection Setup                                                                         | Capture Setup | Phy Tuning       | )           |                   |               |                |                      |

|------------------------------------------------------------------------------------------|---------------|------------------|-------------|-------------------|---------------|----------------|----------------------|

| Module Chassis Slot                                                                      | Fo            | otprint          |             | Link Type         | Link Width    | Link(s)        | Туре                 |

| <b>()</b> 1 5                                                                            | U4321A Slot I | interposer Bot 💌 | 1 Bidirec   | tional up to x8 💌 | x1 💌          | PCIe-105 U43   | 01 PCIeGen3 Analyzer |

| ۲.                                                                                       |               | 1                | Ш           |                   |               |                | >                    |

| Link Naming and La<br>Nam                                                                | e             | Clock Source     | Master Land | e Lane Reversal   | Lane Pola     | rity Inversion | Lane Ord             |

| <ul> <li>All PCI-Express</li> <li>PCIe-105</li> <li>Upstread</li> <li>Downstr</li> </ul> | m             | External 2 🗸     | 0 🗸         | Off V             | Auto No Lanes | Inverted       | Default Spec         |

If you have installed multiple U4301A modules in the chassis, all these modules are listed in the Module section of the tab. You need to select the link type individually for these modules.

4 Select the link width.

| Connection | •        | Capture Setup       |              |                    |               |            |         |

|------------|----------|---------------------|--------------|--------------------|---------------|------------|---------|

| Chassis    |          | Footprint           |              | Link T             | Гуре          | Link Width | Link(s) |

| 1          | 2        | U4322A Bidirectiona | l Full 🐱     | 1 Unidirectional u | up to x16 💌   | x1 🔽       | PCIe-10 |

| <          |          |                     |              |                    |               | x1<br>x2   |         |

| - Link Nan | ning and | Lane Setup          |              |                    |               | x4<br>x8   |         |

|            | Na       | ame                 | Clock Source | Master Lane        | Lane Reversal | x16        |         |

Select the link width that matches the negotiated link width of transmitter and receiver.

If you select the Link Type as **1** Bidirectional upto x8, then you can select the Link Width from x1 to x8. The x16 option is disabled in this case because a U4301A Analyzer module can probe and capture data in both directions with upto eight channels in each direction.

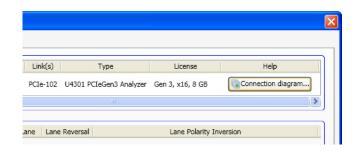

- **5** Verify the connection:

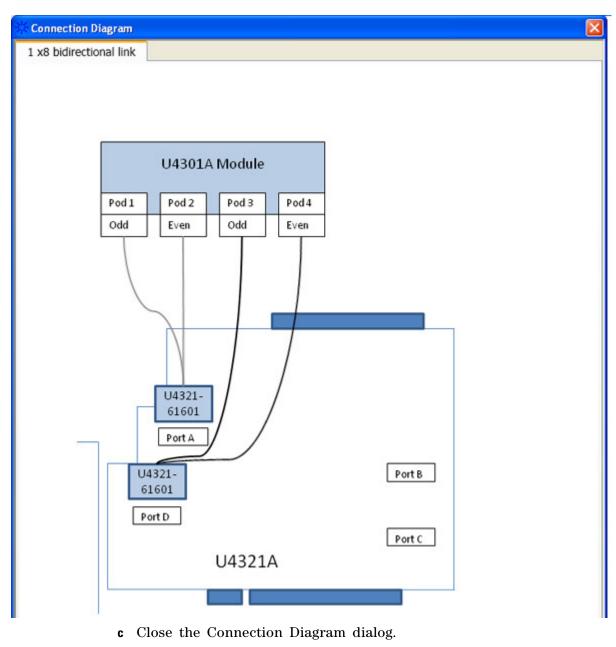

- a Click Connection diagram....

**b** Use the Connection Diagram dialog to verify that your connection setup specification matches the actual device under test connection.

### Specifying the Connection Setup 3

**6** Select the clock source:

### **3** Specifying the Connection Setup

| Connection Set  | up Capture Set         | up                                                                           |            |          |            |

|-----------------|------------------------|------------------------------------------------------------------------------|------------|----------|------------|

| Module          | Link                   | Туре                                                                         | Link Width | Link(s)  |            |

| al Full 🔽       | 1 Unidirectional       | up to x16 🔽                                                                  | x16 🗸      | PCIe-102 | U4301 P    |

| <               |                        |                                                                              |            |          |            |

| - Link Naming a | and Lane Setup<br>Name | Clock Source                                                                 | Master L   | ane Lane | e Reversal |

| All Links       |                        |                                                                              |            |          |            |

| PCIe-           |                        |                                                                              |            |          |            |

| PC              | CTe-102                | Internal<br>Internal<br>External 1<br>External 2<br>External 3<br>External 4 | 0 💌        | Off      | <b>*</b>   |

- **Internal** selects an internal clock source. You should select Internal if the data rate is in the range of 2.5 Gbps or 5 Gbps +/-50 ppm. Note that there is no input clock in this mode.

- External 1/2/3/4 selects an external clock source. You should select External if the device under test uses SSC or the data rate is in the range of 2.5 Gbps +/-300 ppm (+0% / -0.5% if using SSC). The clock rate for external mode should be between 100 MHz +/-300 ppm (+0% / -0.5% if using SSC).

- 7 Select the master lane. You can select any lane as the master lane from the lanes displayed in the Master Lane listbox. The lanes are displayed as per the selected link width. The lane that you select as the master lane is considered the lane for capturing the ordered sets.

| Setup            |                     |              |                                                                                      |                |

|------------------|---------------------|--------------|--------------------------------------------------------------------------------------|----------------|

| Connection Setup | Capture Setup       |              |                                                                                      |                |

| Module           |                     |              |                                                                                      |                |

| t                | Link Typ            | be           | Link Width Li                                                                        | ink(s)         |

| al Full 🐱        | 1 Unidirectional up | to x16 🔽     | x16 🗸 PC                                                                             | Ie-102 U4301 P |

| <                |                     |              |                                                                                      |                |

| Link Naming and  | Lane Setun          |              |                                                                                      |                |

|                  | ame                 | Clock Source | Master Lane                                                                          | Lane Reversal  |

| All Links        |                     |              |                                                                                      |                |

| PCIe-10<br>PCIe  |                     |              |                                                                                      |                |

|                  |                     | Internal 💌   | 0 V<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 | Off 💌          |

8 Specify whether lane reversal is on or off.

| Setup                         |                     |              |            |                  |          |

|-------------------------------|---------------------|--------------|------------|------------------|----------|

| Connection Setup              | Capture Setup       |              |            |                  |          |

| it                            | Link Typ            | e            | Link Width | Link(s)          |          |

| al Full 🔽                     | 1 Unidirectional up | to x16 🐱     | x16 🐱      | PCIe-102         | U4301 PC |

| <                             |                     |              |            |                  |          |

| - Link Naming and I           | ane Setup           |              |            |                  |          |

| Na                            |                     | Clock Source | Master La  | ne Lane          | Reversal |

| <ul> <li>All Links</li> </ul> |                     |              |            |                  |          |

| PCIe-102                      |                     |              |            |                  |          |

| PCIe-1                        | .02                 | Internal 🔽   | 0 🗸        | Off<br>On<br>Off | ~        |

- **9** Specify any lane polarity inversion:

- **a** Click **Auto** or **Manual** to toggle between the types of polarity inversion specification.

When Auto is selected, the polarity of the lanes is set automatically during the initial link training.

**b** When manual selection is chosen, select the lanes that are inverted.

|                 |                     | pe           | Link Width | Link(s)  | Туре             | License                 |             |

|-----------------|---------------------|--------------|------------|----------|------------------|-------------------------|-------------|

| al Full 🐱       | 1 Unidirectional up | o to x16 🐱   | x16 🛩      | PCIe-102 | U4301 PCIeGen3 A | nalyzer Gen 3, x16, 8 ( | зв (        |

| <               |                     |              |            |          |                  |                         |             |

| Link Naming and |                     |              | 1          |          |                  |                         |             |

| All Links       | ame                 | Clock Source | Master L   | ane Lane | Reversal         | Lane Pola               | rity Invers |

| PCIe-102        | 2                   |              |            |          |                  |                         |             |

|                 |                     |              |            |          |                  | All Lanes Inverto       | ed          |

10 The Lane Ordering option lets you perform the ordering of the physical lanes of the link with the logical lanes. You can either retain the **Default** lane ordering which means Lane 0 of the link maps to logical Lane 0 and so on. If you want to map Lane 0 of the link to some other Lane, then select **Custom** option from Lane Ordering and click **Specify** to display the **Custom Lane Ordering** dialog box. In this dialog box, select the lane with which you want to map Lane 0. The number of lanes displayed for lane ordering depend on the selected link width. For

| ietup                                  |                   |                   |             |                                                      |          |                 |                |          |

|----------------------------------------|-------------------|-------------------|-------------|------------------------------------------------------|----------|-----------------|----------------|----------|

| Connection Setup                       | Capture Setup     | Phy Tuning        |             |                                                      |          |                 |                |          |

| - Module                               |                   |                   |             |                                                      |          |                 |                |          |

| Link(s)                                |                   | Footprint         |             | Link Typ                                             | be       | Link Width      | Help           |          |

| OPCIe-105                              | U4321A Slot Inter | poser Both Dir x8 | •           | 1 Unidirectional up                                  | to x16 🐱 | x4 🗸            | Connection dia | agram    |

| <                                      |                   | II                | 10          |                                                      |          |                 |                |          |

| Link Naming and I                      | ane Setun         |                   |             |                                                      |          |                 |                |          |

| Na                                     |                   | Clock Source      | Master Lane | Lane Reversal                                        | Lane Pol | arity Inversion | Lane           | Orderin  |

| <ul> <li>All PCI-Expression</li> </ul> | ss Links          |                   | Case -      |                                                      |          |                 |                |          |

| PCIe-105<br>PCIe-1                     | 05                | External 2 💌      | Lane Re     | m Lane Ordering<br>eordering Mode<br>Ile (Recommende | d) OAdva | nced            | Custom         | Specify. |

|                                        |                   |                   |             | 0 maps to Lane (<br>1 maps to Lane )                 |          |                 |                |          |

| <                                      |                   |                   |             | 2 maps to Lane                                       |          |                 |                |          |

| Rename A                               | dd Folder Delet   | e Folder          |             | 3 maps to Lane                                       |          |                 |                |          |

|                                        |                   |                   |             | ОК                                                   | Help     |                 | K Cancel       | ŀ        |

example, if the link width is selected as x4, then the Lane 0, 1, 2, and 3 are available for lane ordering.

U4301A PCIe Gen3 Analyzer User Guide

4

## **Setting the Capture Options**

The Capture Setup tab in the PCIe Gen3 analyzer's Setup dialog lets you set basic capture options.

1 In the *Agilent Logic Analyzer* application's Overview window, from the PCIe Gen3 analyzer module's drop-down menu, select **Setup>Setup...**.

2 Click the Capture Setup tab.

**3** In the Capture Setup tab, select the appropriate options.

| Setup                              |                                       |                                                |

|------------------------------------|---------------------------------------|------------------------------------------------|

| Connection Setup Ca                | pture Setup Phy Tuning                | ]                                              |

| All PCI-Express Links     PCIe-105 | Capture Setup<br>Capture Memory Depth | 1 MB                                           |

|                                    | Capture Link Speed                    | OGen 1 OGen 2 OGen 3 ⊙Auto (Gen3 -> Gen 1 v ha |

|                                    | Descrambler (Gen1 / Gen               | 2) 💿 Enabled 🔵 Disabled                        |

|                                    | Capture Mode                          | Normal ORaw                                    |

|                                    | L0s Testing                           | Enabled      Disabled                          |

|                                    |                                       |                                                |

| Ctrl+Click to select more t        | han one link.                         | Apply OK Cancel                                |

| Capture<br>Memory Depth | Lets you select the trace memory depth. Deeper traces capture more activity but take longer to save and process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture Link            | <ul> <li>Lets you specify the link speed of the data to be captured:</li> <li>Gen 1 — select this when capturing data on 2.5 Gbps links.</li> <li>Gen 2 — select this when capturing data on 5 Gbps links.</li> <li>Gen 3 — select this option when testing link speed switching scenarios.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Speed                   | On selecting this option, analyzer automatically detects the link speed change and accordingly starts capturing data based on the changed link speed. The Auto option also has a drop-down listbox displayed with it. From this listbox, you can select either Gen1 or Gen2. If you select Gen1 from this listbox, then analyzer prioritizes and captures the Gen 1 ordered sets while switching speed from Gen 3. If you select Gen2 from this listbox, then analyzer prioritizes and captures the Gen 2 ordered sets while switching speed from Gen 3. <li>Based on the selected link speed, the speed LED of the Analyzer pod on which the logical Lane 0 is present will glow. The following color coding is used to interpret the status of the speed LED.</li> <li>Off - This means that the link speed is not detected or not configured.</li> <li>Yellow - This means that the link speed is 2.5 Gb/s.</li> <li>Blue - This means that the link speed is 8 Gb/s.</li> <li>If you selected a fixed speed (Gen1, Gen2, or Gen3), then the speed LED will glow according to the selected speed. If you selected the Auto speed option, then the speed LED will glow according to the selected speed.</li> |

| Descrambler<br>(Gen1 / Gen2) | <ul> <li>Tells the analyzer whether the descrambler algorithm is necessary:</li> <li>Enabled — activates the descrambler algorithm. This algorithm generates the descrambled packet stream from an incoming scrambled packet stream.</li> <li>Disabled — deactivates the descrambler algorithm. Select this option when the DUT is transmitting the non-scrambled data.</li> <li>Garbage data is displayed if this is set incorrectly.</li> </ul>                                                                                                                                                                                                             |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture Mode                 | <ul> <li>Lets you choose between two capture modes:</li> <li>Normal — captures data only when all the configured lanes are out of the Loss of Sync (LOS) condition, that is, each lane has valid data. In this mode, channel bonding occurs when the analyzer encounters the first SKIP ordered set after exiting from the LOs/L1/L2/recover.speed condition.</li> <li>Raw — captures data by each lane. This means, if only one lane is out of the LOS condition, its data is captured in the trace. In this mode, channel bonding may not exist at all. The Raw mode gives you data visibility even when there are significant PHY layer issues.</li> </ul> |

| LOs Testing                  | <ul> <li>Lets you select whether or not the U4301A module will capture packets in the L0s state.</li> <li>Enabled - When you enable the L0s Testing option, the U4301A module captures packets in the L0s state and the power management testing capabilities are enabled and enhanced in terms of : <ul> <li>improvement in locking time</li> <li>faster data capture while coming out of the electrical idle</li> </ul> </li> <li>Disabled - When you disable the L0s Testing option, the power management testing capabilities are available but not enhanced.</li> </ul>                                                                                  |

| NOTE | When testing L0s/L1, ensure that you:                          |

|------|----------------------------------------------------------------|

|      | - set manual lane polarity.                                    |

|      | - select a fixed capture link speed instead of the Auto speed. |

### 4 Setting the Capture Options

U4301A PCIe Gen3 Analyzer User Guide

5

# **Tuning the Analyzer for a Specific DUT**

PCIe Gen3 Tuning Overview 30 Preparing the Analyzer and DUT for Tuning 35 Creating a Physical Layer Tuning File 37 Using the Tuning File in the Logic Analyzer GUI 46 Tuning a Bidirectional Setup 48 Fine Tuning a .ptu File 50 Verifying a Tuning File 52

## PCIe Gen3 Tuning Overview

### What is Tuning

*Tuning* is the process of adjusting Agilent's probing system to remove the effects of different driving silicon, termination silicon (or other termination schemes), imperfect transmission paths, and the fact that the probes may not be in the "ideal" location for receiving a high-speed signal (that is, at the end of the transmission path).

Furthermore, a PCIe Gen3 system will negotiate its own TX Linear Equalization, and you would like to have the largest eye possible. Tuning does not affect either the transmitter or the receiver; it is used only to increase the eye as seen by the U4301 Analyzer module. This process involves getting the system/device-under-test to a stable PCIe Gen3 transmission state which the analyzer then optimizes its own equalizations settings for.

### **How Tuning Works**

For tuning, you run a tuning algorithm with specific parameters to create a physical layer tuning (.ptu) file. This file contains the information necessary to adjust the probing system for a specific device-under-test (DUT). At the 8 Gbps speed, you then need to load this .ptu file into the U4301 Analyzer module's software to have the best possible eye at the Analyzer. If you want to verify that you have the correct .ptu file, there is a verification program that you can run to analyze the eye quality without re-running the tuning algorithm.

For this release of the Agilent PCIe Gen3 software, you can create or verify a .ptu file for tuning using the command line executables provided by Agilent.

### When to Perform Tuning

You should only perform tuning when all of the following conditions are met:

- Poor trace quality which may include red packets, triggers on "Loss of Sync" or "Channel Bonding".

- No Recovery cycles (that is, cannot Trigger on "Any TS") on the target.

- When no existing .ptu files are able to provide robust tracing.

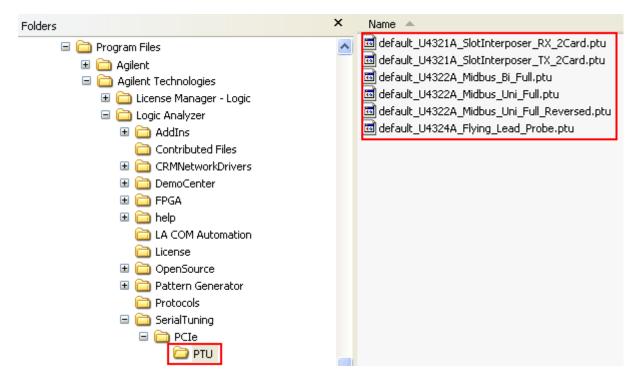

### **Default and User Defined .ptu Files**

A set of default tuning (.ptu) files are provided with the Agilent Logic Analyzer software. These tuning files contain the probe defaults to compensate for the signal impairments associated with the probe. These files are named on the basis of the probe type for which these are created. Based on the probe type you are using, one of these files is used and if the trace quality is clean, you do not need to tune further by creating your own .ptu file. These default .ptu files work fine and support robust tracing in situations where the targets have margin. The following screen displays the location of these default ptu files.

However, if the default .ptu file does not serve the purpose and you find the trace quality to be poor, you can create your own .ptu file with your specific parameters and use it in the Logic Analyzer GUI to perform tuning. You can create a .ptu file using the command line executable provided by Agilent.

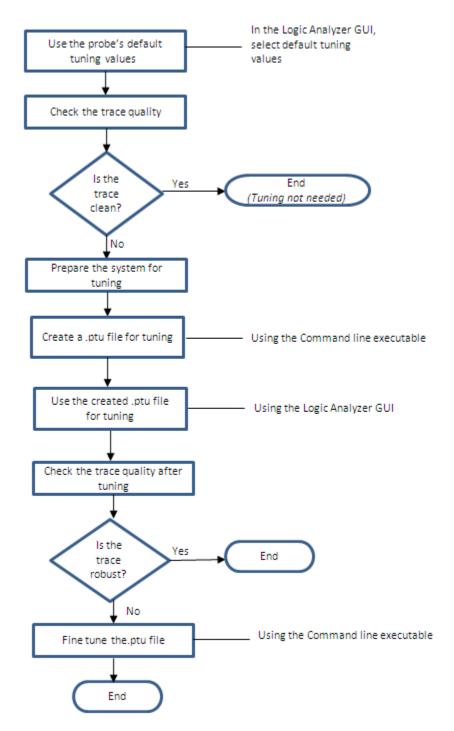

### **Tuning - Broad steps**

The following picture illustrates the broad steps involved in the tuning flow.

All these steps are described in detail in the topics that follow.

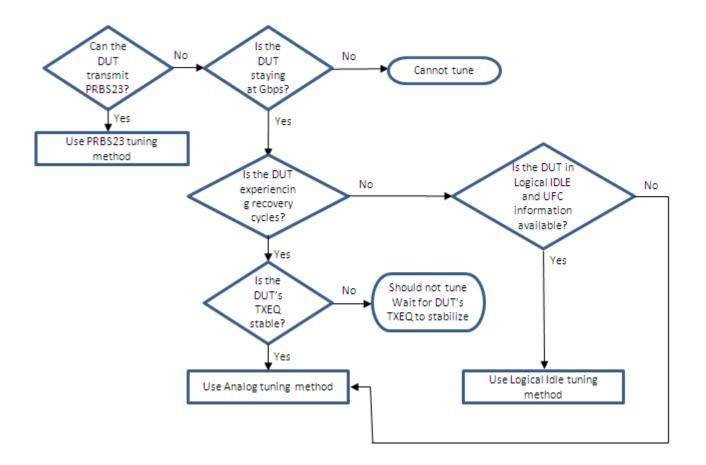

### **Tuning Methods**

While creating the .ptu file using the command line executable, you need to specify the tuning method to be used.

The following tuning methods are currently supported.

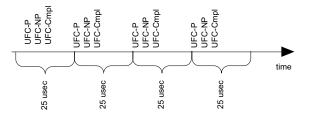

- Logical Idle This method is BER based and aims at checking and minimizing a BER only on the Logical Idle periods. No packet transfer is allowed other than periodic Update Flow Control DLLPs. When using the LIDL tuning, the optional command line parameters such as clocking, inversions, update flow control parameters become relevant. This method is suitable for an initial tuning run as well as for fine tuning previous tuning results.

- AnalogTune This method minimizes the deviations of the observed Vertical Eye characteristics versus the desired Vertical Eye characteristics. The Quality of Results of this tuning method are lesser compared to the BER based tuning methods simply because this method optimizes a surrogate metric for BER. However, from the DUT participation perspective, this method only requires the DUT to stay out of Electrical Idle at 8Gbps. The actual traffic on the bus is irrelevant. When using AnalogTune, the optional command line parameters such as clocking, inversions, and update flow control become irrelevant. To perform AnalogTune, use the --analog command line option while creating the .ptu file. This method is suitable for an initial tuning run.

- **PRBS23** This method is BER based and aims at checking and minimizing a BER on every transmitted bit. You can achieve the highest Quality of Results with this method. However, from the DUT participation perspective, this method requires the DUT to transmit PRBS23. When using the PRBS23 method, the optional command line parameters such as clocking and inversions become relevant but the update flow control parameters are irrelevant. To perform PRBS tuning, use the --prbs command line option while creating the .ptu file. This method is suitable for an initial tuning run.

This method assumes that the PRBS polynomial matches the JBERT's PRBS23  $2^{N-1}$  polynomial:  $D^7 + D^6 + 1 = 0$

• **SyncHeaders** - This method is BER based and aims at checking and minimizing a BER on only the Block Sync headers. This method requires the DUT to transmit Block Sync headers. When using the SyncHeaders method, the optional command line parameter such as clocking is relevant but the inversions and update flow control parameters are irrelevant. To perform SyncHeaders tuning, use the --syncheaders command line option while creating the .ptu file. This method is suitable only for fine tuning and not for an initial tuning run.

To know about how to use these tuning methods, refer to "PCIe Gen3 Tuning Executable and its Usage" on page 37.

### Selecting an appropriate tuning method

You can use the following flowchart to decide which tuning method should be used.

## Preparing the Analyzer and DUT for Tuning

Perform these steps to prepare the system for tuning:

1 Connect the U4301 Analyzer module to the DUT. Refer to the *PCI Express Gen3 Hardware and Probing Guide* to know how to connect Analyzer to the DUT based on your specific probing situation.

Take a note of which probing system you have; you will need to specify this as a required information while running the tuning program:

The following Agilent probing options are supported for use with the Analyzer module.

• U4321A solid slot interposer.

Note that there are four connections on this interposer; the upper two are for the "To Upstream" path (assuming that the card plugged into the top connector of the interposer is the downstream side). The lower two connectors are for the "to Downstream" direction.

• U4322A soft touch midbus 3.0 probe.

Note that there are several supported footprints that define what lanes are at specific physical connections.

• U4324A PCIe Gen3 flying lead probe.

Each of these probes provides support for probing one to four channels of a PCIe link making it a total of 16 channels probing support for a set of four probes.

2 If the Resource Bus connector is connecting two Analyzer modules together (the connector at the left of the modules), remove the Resource Bus Connector and do the tuning of one module at a time.

After you have tuned, you can reconnect the Resource Bus Connector without affecting the tuning.

- 3 Your system must enter L0 at Gen3 speed (8 Gbps).

- **4** For LIDL-based tuning, set up your system so that it is only transmitting the following at 8Gbps:

- a Mostly Logical Idle packets (scrambled zeros).

- **b** Skip Ordered Sets (optional for the tuning to work, but probably necessary for your system).

- **c** Update Flow Control DLLPs (again, optional for the tuning process, but part of the PCIe Gen3 specification even when the link is idle).

- 5 For PRBS tuning, the DUT should be able to transmit PRBS23.

- 6 For Analog tuning, the DUT must stay out of Electrical Idle at 8Gbps and its TXEQ should have stabilized before tuning. If the DUT is

experiencing Recovery cycles, it is likely that it will change its TXEQ to achieve stability.

- 7 Gather the following information about your system:

- **a** The number of lanes in use (1, 2, 4, 8, or 16).

- **b** Which lanes (if any) are inverted by the transmitter.

# **Creating a Physical Layer Tuning File**

After you have prepared your system for tuning, you can create a physical layer tuning (.ptu) file. This file stores the information about the test setup (lane inversions, number of lanes, etc) and the tuning parameters that were discovered during tuning. You use this file in the PCIe Analyzer setup in the Logic Analyzer GUI to tune the system.

You use the command line executable *PCIeGen3PhyTuning.exe* provided by Agilent to create a physical layer tuning file.

# PCIe Gen3 Tuning Executable and its Usage

The following is the usage and a brief description of the required and optional command line options of the PCIe Gen3 tuning executable - *PCIeGen3PhyTuning.exe*.

### Usage

PCIeGen3PhyTuning.exe <Required command line options> <Optional command line options> <PTU file> <PCIe-NNN>

### **Required Command Line Options**

| Command Line option | Value                       | Description                                                                             |  |  |  |

|---------------------|-----------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| lanewidth           | Integer (1, 2, 4, 8, or 16) | The number of lanes that need to be tuned. You can select from 1, 2, 4, 8, or 16 lanes. |  |  |  |

|                     |                             | Examplelanewidth 4                                                                      |  |  |  |

| Command Line option | Value                                                                                                                                                                                                                                                                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| -probetype          | Possible values:<br>• U4321A_To_Upstream<br>• U4321A_To_Downstream_Bidir<br>X8<br>• U4321A_To_Downstream_Bi<br>dirX8<br>• U4322A_Unidirectional_Full<br>• U4322A_Unidirectional_Full<br>Reversed<br>• U4324A_Flying_Lead<br>• U4324A_Flying_Lead_Upstre<br>am_1Card_Bidir_Swizzled<br>• U4324A_Flying_Lead_Down<br>stream_1Card_Bidir_Swizz<br>led | <ul> <li>The type of probe and the configuration in which you are using the probe between the U4301 Analyzer module and DUT. You can specify:</li> <li>U4321A_To_Upstream - Specify this probe type if you are using the top two connectors on the U4321A Solid Slot Interposer card to probe the data in the "To upstream" path.</li> <li>U4321A_To_Downstream - Specify this probe type if you are using the bottom two connectors on the U4321A Solid Slot Interposer card to probe the data in the "To downstream" path.</li> <li>U4321A_To_Upstream_BidirX8 - Specify this probe type if you are using a U4321A Solid Slot Interposer card in a bidirectional configuration and want to tune the lanes associated with the "To upstream" path. In a bidirectional setup, you tune one direction at a time.</li> <li>U4321A_To_Downstream_BidirX8 - Specify this probe type if you are using a U4321A Solid Slot Interposer card in a bidirectional configuration and want to tune the lanes associated with the "To downstream" path. In a bidirectional setup, you tune one direction at a time.</li> <li>U4322A_Unidirectional_Full - Specify this probe type if you are using the U4322A Soft Touch Midbus probe for probing all the 16 lanes in the same direction. Reversed refers to optional lane reversal which is supported for upstream ports.</li> <li>U4322A_Bidirectional_Full - Specify this probe type if you are using the U4322A Soft Touch Midbus probe for probing eight lanes in one direction and the remaining eight lanes in the other direction.</li> <li>U4324A_Flying_Lead - Specify this probe type if you are using the U4322A Soft Touch Midbus probe for probing eight lanes in one direction and the remaining eight lanes in the option and the remaining eight lanes in the other direction.</li> <li>U4324A_Flying_Lead - Specify this probe type if you are using the U4324A Soft Touch Midbus probe for probing eight lanes in one direction and the remaining eight lanes in the same direction.</li> <li>U4324A_Flying_Lead_Downstream_1Card_Bidir_Swizzled - Specify this probe ty</li></ul> |  |  |  |

| Command Line option | Value        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| inversions          | upto 16 bits | A set of 1s and 0s defining which lanes are inverted on your<br>system as seen by the analysis connector.<br>In the value that you specify for theinversions option,<br>"1" means an inverted lane and "0" means an un-inverted lane<br>and Lane 0 is always the last digit in the inversions value. If Lane<br>Reversal is enabled, then provide a value for the<br>inversions option using the pre-reversal lane definition.<br><i>Example</i> - If you specify the following inversions value for a |

|                     |              | eight-lane setup, then it indicates that lanes 0,1,and 4 are inverted in this setup.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     |              | inversions 00010011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     |              | <b>Note:</b> Theinversions command line option is irrelevant<br>if you are performing the Analog tuning (using theanalog<br>command line option). For inversion-sensitive tuning methods<br>such as Logical Idle and PRBS23, valid inversion values are<br>required.                                                                                                                                                                                                                                   |

# **Optional Command Line Options**

| Command Line option | Value                  | Description                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|---------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| analog              | Not applicable         | Use this option to specify that the AnalogTune method should be<br>used for tuning. This option requires the DUT to stay out of<br>Electrical IDLE at 8 Gbps.<br>If you use this command line option, then theufctime,<br>ufcburstlength,extclk, andinversions<br>command line options do not have any significance. |  |  |  |  |

| prbs                | Not applicable         | Use this option to specify that the PRBS23 method should be<br>used for tuning. This option requires the DUT to transmit PRBS23.<br>If you use this command line option, then theextclk and<br>inversions command line options are relevant but<br>ufctime andufcburstlength do not have any<br>significance.        |  |  |  |  |

| ufctime             | Integer (microseconds) | <ul> <li>The minimum time between Update Flow Control DLLP bursts, in microseconds See:</li> <li>"How "Minimum Time Between UFCs" and "UFC Burst Length" is Used in LIDL Tuning" on page 44</li> <li>"Understanding "Minimum Time Between UFCs" and "UFC Burst Length"" on page 43</li> </ul>                        |  |  |  |  |

| Command Line option | Value                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|---------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ufcburstlength      | Integer (between 1 and 15)<br>The default is 3.               | <ul> <li>The number of back-to-back Update Flow Control DLLPs in a burst. See:</li> <li>"How "Minimum Time Between UFCs" and "UFC Burst Length" is Used in LIDL Tuning" on page 44</li> <li>"Understanding "Minimum Time Between UFCs" and "UFC Burst Length"" on page 43</li> </ul>                                                                                                                                                                                                                                                                                  |  |  |  |

| extclk              | 1 to 4                                                        | A number representing the Analyzer module's Pod that the external reference clock is probed on. If you are using the U4321A probe, then this choice must be Pod 2.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

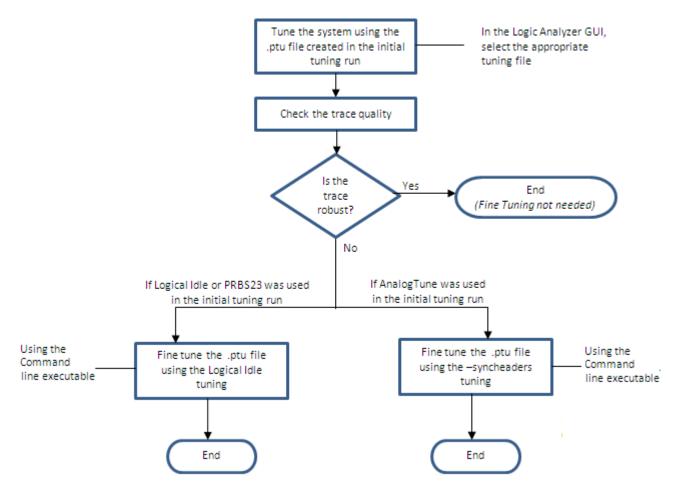

| fine                | Not applicable                                                | This option fine tunes the results of a previous tuning. It starts with the results of a previously created .ptu file and refines and stores the results in the .ptu file specified as output. Therefore, when you use thefine option, you must load a previously created .ptu file using theloadptu option. This fine tuning can take quite a bit of time. Refer to "Fine Tuning a .ptu File" on page 50 to know more about fine tuning.                                                                                                                             |  |  |  |

| loadptu             | <name and="" location="" of="" the<br="">.ptu file&gt;</name> | Use this option when you want to load the results of a previously created tuning file.<br><b>Example</b> loadptu C:\PCIe_tuning_files\<br>DownstreamAnalog.ptu<br>This option is particularly significant when you are creating a tuning file for a bidirectional setup or when you are fine tuning the results of a previous tuning. You can also use this option to speed up the tuning basing the tuning on a previous run.<br>See "Tuning a Bidirectional Setup" on page 48 and "Fine Tuning a .ptu File" on page 50 to know more about the usage of this option. |  |  |  |

| description         | <filename></filename>                                         | A file describing the test environment setup. If you do not specify<br>any file name, then the tuning program prompts you to type the<br>test environment description.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

# <PTU File>

The name and location that you want to provide for the .ptu file. The command to invoke the tuning executable fails if you do not provide the name and location of the tuning file. Ensure that you use explicit file paths while specifying the name and location of the .ptu file.

### Example

C:\PUT\_File\PCIeGen3\_Downstream\_PTU.ptu

### <PCIe-NNN>

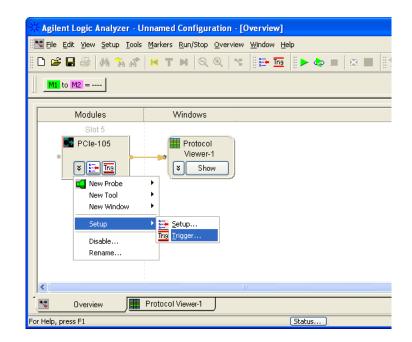

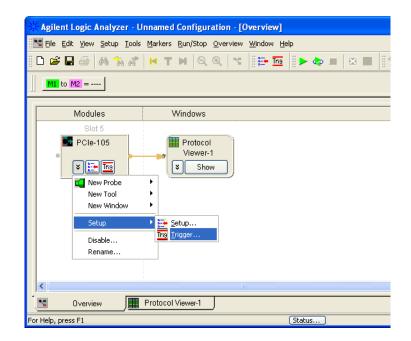

The name of the U4301 Analyzer module for which you want to create the tuning file. This is the same name with which the U4301 Analyzer module is represented in the Logic Analyzer GUI's Overview tab. For example, PCIe-101.

|    | Agile          | ent L        | ogic <i>l</i> | Analy         | zer - U         | nnam          | ed Co         | onfigu  | ratio       | n - [C | )vervie        | w]             |     |

|----|----------------|--------------|---------------|---------------|-----------------|---------------|---------------|---------|-------------|--------|----------------|----------------|-----|

|    | 😼 <u>F</u> ile | <u>E</u> dit | <u>V</u> iew  | <u>S</u> etup | o <u>T</u> ools | <u>M</u> arke | rs <u>R</u> i | ın/Stop | <u>O</u> ve | rview  | <u>W</u> indov | ı <u>H</u> elp | 2   |

|    | D 🖻            | ;            | 3             | <b>/4</b> 1   | ā at            | M             | T Þ           | I Q     | Ð           |        | ## 0           | ## 1           | 'i9 |

|    | M1             | to M         | 2 =           |               |                 |               |               |         |             |        |                |                |     |

|    |                |              | Modul         |               |                 |               | \0.6          | ndows   |             |        |                |                |     |

|    |                |              |               |               |                 |               | 0011          | 100005  |             |        |                |                |     |

|    |                |              | Slot          | t 5           |                 |               |               |         |             |        |                |                |     |

|    |                | -            | PCle-         | 105           |                 |               | 1             | Protoco | I           | 1      |                |                |     |

|    |                |              |               |               |                 |               |               | viewer- | ·1          |        |                |                |     |

|    |                |              | * 📴           | Tris          |                 |               | ×             | Sho     | W           |        |                |                |     |

|    |                |              |               |               |                 |               | $\tilde{c}$   |         |             | 3      |                |                |     |

|    |                |              |               |               |                 |               |               |         |             |        |                |                |     |

|    |                |              |               |               |                 |               |               |         |             |        |                |                |     |

| ,  | 5              | 0            | )vervie       | w             |                 | Proto         | ol Vie        | wer-1   | J           |        |                |                |     |

| Fo | r Help,        | press        | F1            |               |                 |               |               |         |             |        |                |                |     |

The command to invoke the tuning executable fails if you do not provide the name of the Analyzer module.

### **Tuning Executable Usage - Example**

```

PCIeGen3PhyTuning.exe --lanewidth 8 --probetype

U4321A_To_Upstream_BidirX8 --prbs --inversions 0011000 -extclk 2 C:\

PTU_Files\Upstream.ptu PCIe-105

```

In this example, the tuning executable has been invoked to create a tuning file named Upstream.ptu at C:\PTU\_Files\ for a bidirectional probing setup configured using the U4321A solid slot interposer card. This command aims at creating a tuning file for tuning only the lanes in the "To Upstream" direction.

### To create a physical tuning file

Perform these steps on the host PC that is physically connected to the U4301 Analyzer module.

- 1 Exit the Agilent Logic Analyzer application if it is currently active.

- 2 Start the Agilent Logic Analyzer application.

This is done to ensure that all of the default settings in the analyzer software are used.

- **3** Open a Command prompt.

- **4** Navigate to the folder where the command line executable (*PCIeGen3PhyTuning.exe*) used for tuning is located. This executable is located at:

<Install location of Logic Analyzer>\SerialTuning\PCIe\Scripts

For example, C: \Program Files\Agilent Technologies\Logic Analyzer\SerialTuning\PCIe \Scripts